# VTM™ Current Multiplier

VTM2308S60Z0825T00

# Sine Amplitude Converter (SAC™)

#### **Features & Benefits**

- 2250V<sub>DC</sub> Galvanically Isolated Output Voltage

- 40 5V<sub>DC</sub> 25A Current Multiplier

- Operating from Standard 48V or 24V PRM™ Regulators

- Up to 60 Volts DC Input

- K of 1/8 Provides up to 25A DC Output Current

- Up to 64x Reduction in Output Capacitance Requirements

- High Efficiency (>95%) Reduces System Power Consumption

- High Density (430A/in<sup>3</sup>)

- Vicor VTM2308 SM-ChiP™ Package Enables Low-Impedance Interconnect to System Board

- Provides Enable / Disable Control, Internal Temperature Monitoring

- ZVS / ZCS Resonant Sine Amplitude Converter Topology

- Can Be Used in Parallel for High-Current Applications

#### **Typical Applications**

- CPU, GPU & ASIC Core Rails

- Computing and Telecom Systems

- Automated Test Equipment

- Communications Systems

| Product Ratings                |                                  |  |  |  |  |  |  |

|--------------------------------|----------------------------------|--|--|--|--|--|--|

| $V_{IN} = 0 - 60V$             | I <sub>OUT</sub> = 25A (Nominal) |  |  |  |  |  |  |

| $V_{OUT} = 0 - 7.5V$ (No Load) | K = 1/8                          |  |  |  |  |  |  |

## **Product Description**

The Vicor VTM2308 SM-ChiP current multiplier is an isolated, high-efficiency Sine Amplitude Converter (SAC) designed to deliver low-voltage output. The Sine Amplitude Converter offers a low AC impedance beyond the bandwidth of most downstream regulators; therefore capacitance normally at the load can be located at the input to the Sine Amplitude Converter. Capacitance at the input of the VTM is reflected to the output by a factor of (1/K)², resulting in savings of board area, materials and total system cost.

Vicor SM-ChiP packages are compatible with standard pick-and-place assembly processes. The co-molded ChiP package provides enhanced thermal management due to a large thermal interface area and superior thermal conductivity. The high conversion efficiency of the VTM increases overall system efficiency and lowers operating costs compared to conventional approaches.

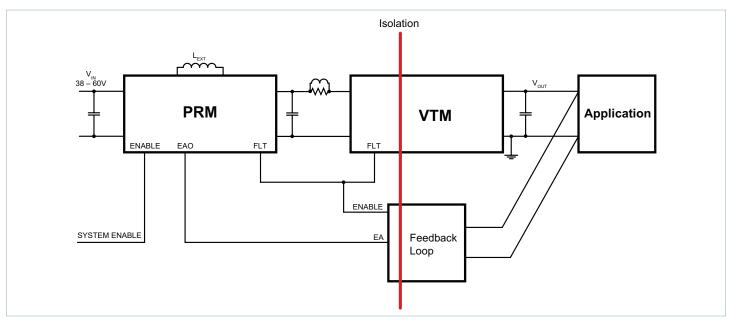

When powered by a PRM, the VTM enables the utilization of Factorized Power Architecture<sup>TM</sup>, which provides efficiency and size benefits by lowering conversion and distribution losses and promoting high-density point-of-load conversion.

# **Typical Application**

$\textit{Typical application: Isolated DC-DC PoL converter using Factorized Power Architecture} \\ \textbf{^{TM}}$

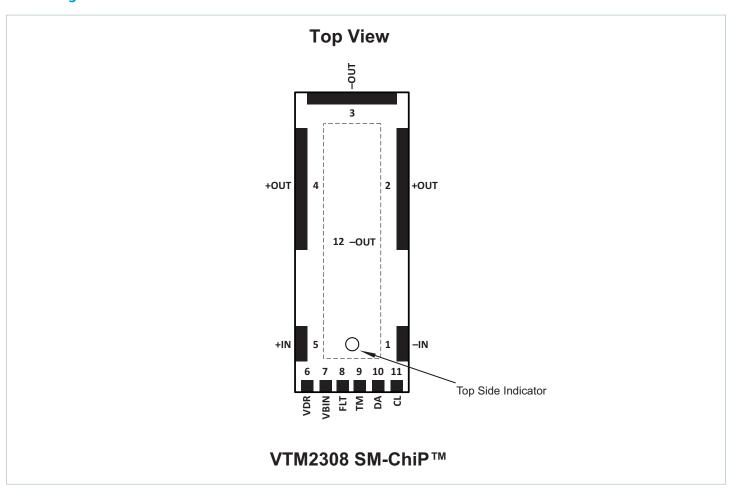

# **Pin Configuration**

# **Pin Descriptions**

| Signal Name | Pin<br>Number        | Туре                   | Description                                          |  |  |  |

|-------------|----------------------|------------------------|------------------------------------------------------|--|--|--|

| -IN         | 1                    | INPUT POWER<br>RETURN  | Negative input power terminal                        |  |  |  |

| +OUT        | 2, 4                 | OUTPUT POWER           | Positive output power terminal                       |  |  |  |

| -OUT        | 3, 12 <sup>[a]</sup> | OUTPUT POWER<br>RETURN | Negative output power terminal                       |  |  |  |

| +IN         | 5                    | INPUT POWER            | Positive input power terminal                        |  |  |  |

| VDR         | 6                    | INPUT                  | Low-voltage bias input, Powertrain controller supply |  |  |  |

| VBIN        | 7                    | NO CONNECT             | Factory use only                                     |  |  |  |

| FLT         | 8                    | INPUT / OUTPUT         | DISABLE pin; PRM™ SM-ChiP fault management pin       |  |  |  |

| TM          | 9                    | OUTPUT                 | Temperature monitor / Fault Flag                     |  |  |  |

| DA          | 10                   | No Connect             | Factory use only                                     |  |  |  |

| CL          | 11                   | No Connect             | Factory use only                                     |  |  |  |

<sup>[</sup>a] Represents product top and bottom conductive, mechanical plating. Reference product outline for additional details.

# **Part Ordering Information**

| Part Number                         | Part Number Temperature Grade |                 | Tray Size         |

|-------------------------------------|-------------------------------|-----------------|-------------------|

| VTM2308S60Z0825 <b>T</b> 0 <b>0</b> | <b>T</b> = -40 to 125°C       | <b>0</b> = None | 88 parts per tray |

All products shipped in JEDEC standard high-profile (0.400" thick) trays (JEDEC Publication 95, Design Guide 4.10).

## **Absolute Maximum Ratings**

The absolute maximum ratings below are stress ratings only. Operation at or beyond these maximum ratings can cause permanent damage to the device.

| Parameter                        | Comments | Min  | Max  | Unit            |

|----------------------------------|----------|------|------|-----------------|

| VDR to -IN                       |          | -0.3 | 5.5  | $V_{DC}$        |

| FLT to -IN                       |          | -0.3 | 5.5  | $V_{DC}$        |

| TM to -IN                        |          | -0.3 | 5.5  | $V_{DC}$        |

| +IN to -IN                       |          | -1.0 | 75   | $V_{DC}$        |

| +IN / -IN to +OUT / -OUT (Hipot) |          |      | 2250 | $V_{DC}$        |

| +OUT to -OUT                     |          | -1.0 | 25   | V <sub>DC</sub> |

# **Electrical Specifications**

Specifications apply over all line and load conditions unless otherwise noted; **boldface** specifications apply over the temperature range of  $-40^{\circ}\text{C} \leq T_{\text{INTERNAL}} \leq 125^{\circ}\text{C}$  (T-Grade). All other specifications are at  $T_{\text{INTERNAL}} = 25^{\circ}\text{C}$  unless otherwise noted. Electrical performance data includes VDR bias losses where appropriate.

| Attribute                 | Symbol               | Conditions / Notes                                                     | Min          | Тур  | Max | Unit            |  |

|---------------------------|----------------------|------------------------------------------------------------------------|--------------|------|-----|-----------------|--|

|                           |                      |                                                                        |              |      |     |                 |  |

|                           |                      | Powertrain                                                             |              |      |     |                 |  |

| Input Voltage Range       | V <sub>IN</sub>      | VDR applied                                                            | <b>0</b> [p] |      | 60  | V <sub>DC</sub> |  |

| V <sub>IN</sub> Slew Rate | dV <sub>IN</sub> /dt |                                                                        |              |      | 1   | V / µs          |  |

|                           |                      | V <sub>IN</sub> = 40V                                                  |              |      | 1.9 |                 |  |

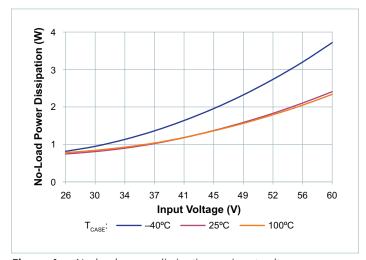

| No Lord Davis Dissipation | D.                   | $V_{IN} = 0 - 60V$                                                     |              |      | 4.5 | 10/             |  |

| No-Load Power Dissipation | P <sub>NL</sub>      | $V_{IN} = 40V$                                                         |              | 1.2  | 1.4 | W               |  |

|                           |                      | V <sub>IN</sub> = 0 - 60V                                              |              |      | 3.1 |                 |  |

| DC Input Current          | I <sub>IN_DC</sub>   | Steady state                                                           |              |      | 3.3 | А               |  |

| Transfer Ratio            | K                    | $K = V_{OUT} / V_{IN}$                                                 |              | 1/8  |     | V/V             |  |

| Output Voltage            | V <sub>OUT</sub>     | $V_{OUT} = V_{IN} \bullet K - I_{OUT} \bullet R_{OUT}, I_{OUT} = 0A$   | 0            |      | 7.5 | V               |  |

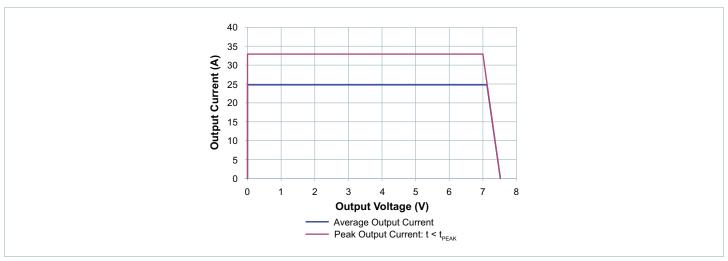

| Output Current (Average)  | I <sub>OUT_AVG</sub> | Steady state                                                           |              |      | 25  | А               |  |

| Output Current (Peak)     | I <sub>OUT_PK</sub>  | t <sub>PEAK</sub> ≤ 10ms, I <sub>OUT_AVG</sub> < 25A, duty cycle = 25% |              |      | 33  | А               |  |

| Output Power (Average)    | P <sub>OUT_AVG</sub> | I <sub>OUT_AVG</sub> ≤ 25A                                             |              |      | 187 | W               |  |

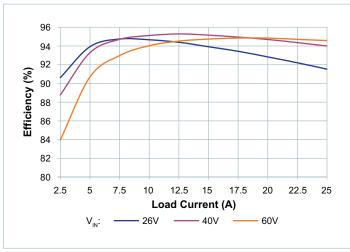

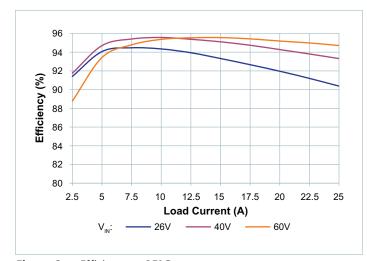

|                           |                      | V <sub>IN</sub> = 40V, I <sub>OUT</sub> = 25A                          | 92.3         | 93.4 |     |                 |  |

| Efficiency (Ambient)      | $\eta_{AMB}$         | V <sub>IN</sub> = 26 – 60V, I <sub>OUT</sub> = 25A                     | 87.9         |      |     | %               |  |

|                           |                      | V <sub>IN</sub> = 40V, I <sub>OUT</sub> = 12.5A                        | 94.7         | 95.3 |     |                 |  |

$<sup>^{[</sup>b]}$  VTM operation tested at 26V $_{IN}$  minimum. VTM operation guaranteed by design 0 – 26V $_{IN}$ .

# **Electrical Specifications (Cont.)**

Specifications apply over all line and load conditions unless otherwise noted; **boldface** specifications apply over the temperature range of  $-40^{\circ}\text{C} \leq T_{\text{INTERNAL}} \leq 125^{\circ}\text{C}$  (T-Grade). All other specifications are at  $T_{\text{INTERNAL}} = 25^{\circ}\text{C}$  unless otherwise noted. Electrical performance data includes VDR bias losses where appropriate.

| Attribute                                 | Attribute Symbol Conditions / Notes |                                                                                           | Min  | Тур  | Max  | Unit              |

|-------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|-------------------|

|                                           |                                     |                                                                                           |      |      |      |                   |

|                                           |                                     | Powertrain (Cont.)                                                                        |      |      |      |                   |

| Efficiency (Hot)                          | $\eta_{\text{HOT}}$                 | T <sub>INT</sub> = 100°C, V <sub>IN</sub> = 40V, I <sub>OUT</sub> = 25A                   | 91.0 | 92.4 |      | %                 |

| Efficiency (Over Load Range)              | η <sub>30%</sub>                    | 7.5A < I <sub>OUT</sub> < 25A, V <sub>IN</sub> = 40V                                      | 91   |      |      | %                 |

| Output Resistance (Cold)                  | R <sub>OUT_COLD</sub>               | $T_{INT} = -40$ °C, $I_{OUT} = 25A$                                                       | 6.4  | 8.5  | 10.7 | mΩ                |

| Output Resistance (Ambient)               | R <sub>OUT_AMB</sub>                | T <sub>INT</sub> = 25°C, I <sub>OUT</sub> = 25A                                           | 8.4  | 10.8 | 13.1 | mΩ                |

| Output Resistance (Hot)                   | R <sub>OUT_HOT</sub>                | T <sub>INT</sub> = 100°C, I <sub>OUT</sub> = 25A                                          | 9.2  | 12.5 | 15.8 | mΩ                |

| Switching Frequency                       | F <sub>SW</sub>                     |                                                                                           | 1.79 | 1.86 | 2.00 | MHz               |

| Output Ripple Frequency                   | F <sub>SW_RP</sub>                  |                                                                                           | 3.58 | 3.72 | 4.00 | MHz               |

| Output Voltage Ripple                     | V <sub>OUT_PP</sub>                 | $C_{OUT} = 0\mu F$ , $I_{OUT} = 25A$ , $V_{IN} = 40V$ , $20MHz~BW$                        |      | 300  | 600  | mV <sub>P-P</sub> |

| Output Inductance (Parasitic)             | L <sub>OUT_PAR</sub>                | Frequency up to 30MHz, simulated leads model                                              |      | 270  |      | рН                |

| Output Capacitance (Internal)             | C <sub>OUT_INT</sub>                | Effective value at 5V <sub>OUT</sub>                                                      |      | 20   |      | μF                |

|                                           |                                     |                                                                                           |      |      |      |                   |

|                                           |                                     | Protection                                                                                |      |      |      |                   |

| Overvoltage Lockout                       | V <sub>IN_OVLO+</sub>               | VTM latches after fault                                                                   | 61.6 | 64.8 | 68   | V                 |

| Overvoltage Lockout<br>Response Time      | t <sub>OVLO</sub>                   | Internal digital control                                                                  |      | 0.5  |      | μs                |

| Output Overcurrent Trip                   | I <sub>OCP</sub>                    | VTM latches after fault                                                                   | 40   | 46   | 65   | А                 |

| Short Circuit Protection Trip Current     | I <sub>SCP</sub>                    | VTM latches after fault                                                                   | 40   |      |      | А                 |

| Output Overcurrent Blanking Time          | t <sub>OCP</sub>                    | Internal digital blanking timer                                                           |      | 12   |      | ms                |

| Short Circuit Protection<br>Response Time | t <sub>SCP</sub>                    | Duration from detection to cessation of switching, cycle-by-cycle short-circuit detection |      | 0.1  |      | μs                |

| Overtemperature Shut-Down<br>Set Point    | T <sub>OT</sub>                     |                                                                                           | 125  | 135  | 145  | °C                |

| Overtemperature Shut-Down<br>Hysteresis   | T <sub>OT_HYS</sub>                 |                                                                                           |      | 25   |      | °C                |

| Reverse Inrush Current Protection         |                                     | Reverse inrush protection is enabled for this product                                     |      |      |      |                   |

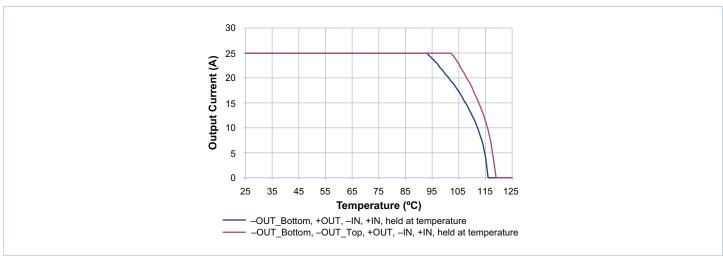

Figure 1 — Specified thermal operating area, high line, full load

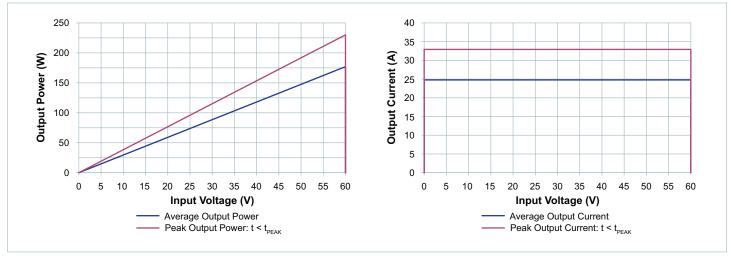

**Figure 2** — Specified electrical operating area, R<sub>OUT</sub> max hot

Figure 3 — Specified electrical operating area

## **Signal Characteristics**

Specifications apply over all line and load conditions unless otherwise noted; **boldface** specifications apply over the temperature range of  $-40^{\circ}\text{C} \le T_{\text{INTERNAL}} \le 125^{\circ}\text{C}$  (T-Grade). All other specifications are at  $T_{\text{INTERNAL}} = 25^{\circ}\text{C}$  unless otherwise noted. Electrical performance data includes VDR bias losses where appropriate.

#### **VTM Driver Supply: VDR**

- Used to wake up internal control circuitry.

- VDR voltage must be continuously applied and must be within specified limit for proper operation.

| Signal Type | State        | Attribute                  | Symbol               | Conditions / Notes                                              | Min  | Тур | Max  | Unit |

|-------------|--------------|----------------------------|----------------------|-----------------------------------------------------------------|------|-----|------|------|

|             |              | VDR Voltage (External)     | $V_{VDR\_EXT}$       |                                                                 | 4.85 |     | 5.35 | V    |

|             | Steady       | VDR Current Draw           | 1                    | $VDR = 5.1V$ , $V_{IN} = 40V$ , $T_{INT} = 100$ °C              |      | 92  | 116  | νο Λ |

|             |              | VDR Current Draw           | $I_{VDR}$            | Fault mode. VDR > 4.85V                                         |      | 17  |      | mA   |

| Analog      | Start Up     | VDR Inrush Current         | I <sub>INR_VDR</sub> | VDR = 5.35V, dVDR / dt = 1V/μs                                  |      |     | 2    | А    |

| Input       | Transitional | VDR to TM Turn-On Delay    | t <sub>ON</sub>      | $V_{IN}=0$ V, FLT floating, VDR applied, $C_{FLT}=0\mu F$       | 23   | 28  | 34   | ms   |

|             |              | VDR to FLT Delay           | t <sub>VDR_FLT</sub> | VDR = 4.85V to FLT high, $V_{IN}$ = 0V, dVDR / dt = 1V/ $\mu$ s |      | 0.2 | 0.3  | ms   |

|             |              | VDR Capacitance (Internal) | C <sub>VDR_INT</sub> | VDR = 0V                                                        |      | 2.2 |      | μF   |

#### **Fault Management: FLT**

- The FLT pin disables the VTM module. When held below 1V, the VTM module will be disabled.

- FLT pin outputs 4.7V minimum during normal operation. FLT pin is equal to 0V minimum during fault mode given VDR > 4.85V and floating FLT pin.

- Module will shut down when pulled low with an impedance less than  $25k\Omega$ .

- A 100pF maximum filtering capacitor can be used on this pin.

| Signal Type                   | State    | Attribute                 | Symbol                | Conditions / notes                                                            | Min  | Тур | Max | Unit |

|-------------------------------|----------|---------------------------|-----------------------|-------------------------------------------------------------------------------|------|-----|-----|------|

| Analog Output Steady Start Up | C+l      | FLT Voltage               | $V_{FLT}$             |                                                                               |      | 5   |     | V    |

|                               | Steady   | FLT Source Current        | I <sub>FLT_OP</sub>   |                                                                               |      |     | 10  | μΑ   |

|                               | Start Up | FLT Source Current        | I <sub>FLT_EN</sub>   |                                                                               |      |     | 10  | μΑ   |

|                               | Enable   | FLT Voltage               | $V_{FLT\_EN}$         |                                                                               |      | 3   | 4   | V    |

| Digital                       | Disable  | FLT Voltage (Disable)     | $V_{FLT\_DIS}$        |                                                                               | 1    | 2   |     | V    |

| Input/<br>Output              |          | FLT Resistance (External) | $R_{FLT\_EXT}$        | Connected to –IN. Min value to guarantee start up (open circuit OK), FLT > 4V | 1600 |     |     | kΩ   |

|                               |          | FLT Sink Capability       | I <sub>FLT_SINK</sub> | Fault State                                                                   | 1    |     |     | mA   |

#### **Temperature Monitor: TM**

- ullet The TM pin monitors the internal temperature of the VTM controller IC within an accuracy of  $\pm 5^{\circ}$ C.

- Can be used as a "Power Good" flag to verify VTM module operation.

- The TM pin has a room temperature setpoint of 3V and approximate gain of 10mV/K.

- Output drives Temperature Shut-down comparator.

| Signal Type  | State        | Attribute                 | Symbol                | Conditions / notes                                  | Min  | Тур  | Max  | Unit |

|--------------|--------------|---------------------------|-----------------------|-----------------------------------------------------|------|------|------|------|

|              |              | TM Voltage                | $V_{TM}$              | $T_{INT}$ controller = 27°C, $I_{TM}$ < 100 $\mu$ A | 2.85 | 3    | 3.15 | V    |

| Analog       | Ctoody       | TM Source Current         | I <sub>TM</sub>       |                                                     |      |      | 100  | μΑ   |

| Output       | Steady       | TM Gain                   | $A_{TM}$              |                                                     |      | 10   |      | mV/K |

|              |              | TM Voltage Ripple         | $V_{TM\_PP}$          | $C_{TM} = 0F$ , $V_{IN} = 40V$ , $I_{OUT} = 25A$    |      | 150  | 350  | mV   |

|              | Steady       | TM Disable Voltage        | $V_{TM\_DIS}$         | PGOOD deasserted                                    |      | 0.2  |      | V    |

| Digital      |              | TM Enable Source Current  | I <sub>TM_FLT</sub>   | $V_{TM} > 1V$                                       | 20   |      |      | mA   |

| Output       |              | TM Fault Sink Current     | I <sub>TM_FAULT</sub> | $V_{TM} \le 0.1V$ , Fault state                     | 1    |      |      | mA   |

| (Fault Flag) | Transitional | TM Capacitance (External) | $C_{TM\_EXT}$         |                                                     |      |      | 100  | рF   |

|              | iransitional | TM Fault Response Time    | t <sub>FR_TM</sub>    | From fault detection to TM driven low               |      | 0.02 |      | μs   |

## **Application Characteristics**

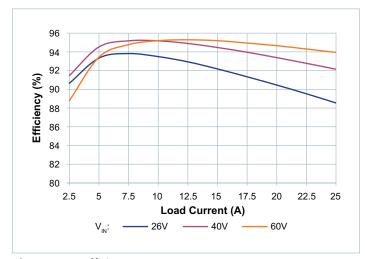

The following values are typical of an application environment. Electrical performance data includes VDR bias losses where appropriate. See associated figures for general trend data.

Figure 4 — No-load power dissipation vs. input voltage

Figure 6 — Efficiency at -40°C case temperature

Figure 8 — Efficiency at 25°C case temperature

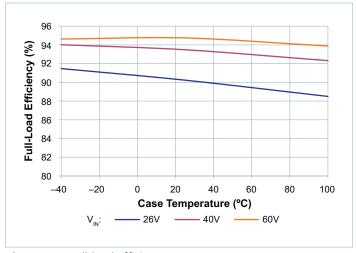

Figure 5 — Full-load efficiency vs. case temperature

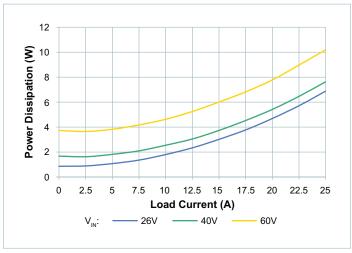

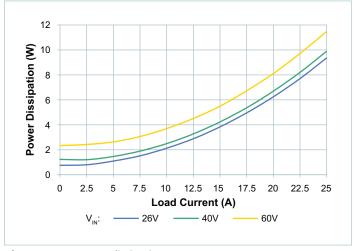

**Figure 7** — Power dissipation at -40°C case temperature

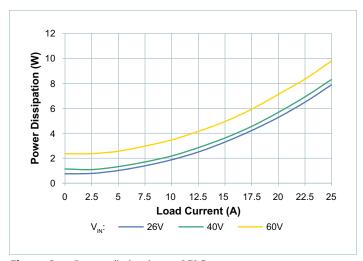

Figure 9 — Power dissipation at 25°C case temperature

## **Application Characteristics (Cont.)**

The following values are typical of an application environment. Electrical performance data includes VDR bias losses where appropriate. See associated figures for general trend data.

Figure 10 — Efficiency at 100°C case temperature

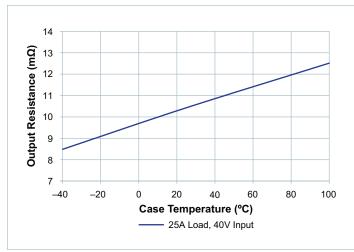

**Figure 12** — Output resistance ( $R_{OUT}$ ) vs. case temperature at nominal input voltage

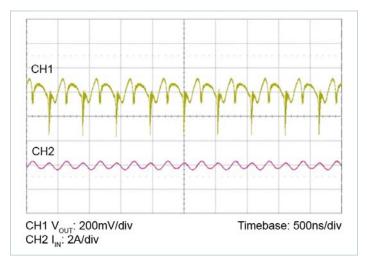

**Figure 14** — Full-load ripple, 100μF C<sub>IN</sub>; no external C<sub>OUT</sub>.

Figure 11 — Power dissipation at 100°C case temperature

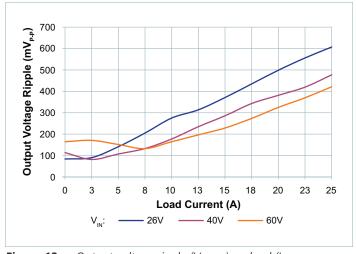

**Figure 13** — Output voltage ripple ( $V_{RIPPLE}$ ) vs. load ( $I_{OUT}$ ); no external  $C_{OUT}$ .

## **General Characteristics**

Specifications apply over all line and load conditions unless otherwise noted; **boldface** specifications apply over the temperature range of  $-40^{\circ}\text{C} \leq T_{\text{INTERNAL}} \leq 125^{\circ}\text{C}$  (T-Grade). All other specifications are at  $T_{\text{INTERNAL}} = 25^{\circ}\text{C}$  unless otherwise noted.

| Attribute                      | Symbol              | Conditions / Notes                                                                              | Min                | Тур                 | Max           | Unit                  |

|--------------------------------|---------------------|-------------------------------------------------------------------------------------------------|--------------------|---------------------|---------------|-----------------------|

|                                |                     |                                                                                                 |                    |                     |               |                       |

|                                |                     | Mechanical                                                                                      | 1                  |                     |               |                       |

| Length                         | L                   |                                                                                                 | 22.7 [0.894]       | 22.83 [0.899]       | 22.96 [0.904] | mm [in]               |

| Width                          | W                   |                                                                                                 | 8.39 [0.33]        | 8.52 [0.335]        | 8.65 [0.34]   | mm [in]               |

| Height                         | Н                   |                                                                                                 | 4.775 [0.188]      | 4.9 [0.193]         | 5.025 [0.198] | mm [in]               |

| Volume                         | Vol                 | No heat sink                                                                                    |                    | 0.953 [0.058]       |               | cm³ [in³]             |

| Weight                         | W                   |                                                                                                 |                    | 3.670 [0.1295]      |               | g [oz]                |

| Exterior Package Plating       |                     | Nickel                                                                                          | 3                  |                     | 6             | 1100                  |

| exterior rackage riatility     |                     | Gold                                                                                            | 0.08               |                     | 0.2           | μm                    |

|                                |                     |                                                                                                 |                    |                     |               |                       |

|                                | 1                   | Thermal                                                                                         | I                  | I                   |               |                       |

| Operating Temperature          | T <sub>INT</sub>    | T-Grade                                                                                         | -40                |                     | 125           | °C                    |

| Thermal Capacity               |                     |                                                                                                 |                    | 2.5                 |               | Ws / °C               |

|                                |                     |                                                                                                 |                    |                     |               |                       |

|                                | 1                   | Assembly                                                                                        | I                  | I                   |               |                       |

| Peak Compressive Force         |                     |                                                                                                 |                    |                     | 5             | lbs                   |

| Applied to Case (Z-Axis)       |                     |                                                                                                 |                    |                     | 16.6          | lbs / in <sup>2</sup> |

| Storage Temperature            | T <sub>ST</sub>     | T-Grade                                                                                         | -55                |                     | 125           | °C                    |

| ESD Withstand                  | ESD <sub>HBM</sub>  | Human Body Model,<br>(JEDEC JS-001-2012 Table 2B) Class 1C                                      | 2000               |                     |               | V <sub>DC</sub>       |

| 235 Willisteria                | ESD <sub>CDM</sub>  | Charged Device Model,<br>(JESD22-C101E) Class III                                               | 500                |                     |               | v DC                  |

|                                |                     |                                                                                                 |                    |                     |               |                       |

|                                |                     | Soldering                                                                                       | ı                  | I                   |               |                       |

| Peak Temperature During Reflow |                     | MSL 4                                                                                           |                    |                     | 245           | °C                    |

|                                |                     |                                                                                                 |                    |                     |               |                       |

|                                | I                   | Safety                                                                                          |                    |                     |               |                       |

| Isolation Voltage (Hipot)      | V <sub>HIPOT</sub>  |                                                                                                 | 2250               |                     |               | V                     |

| Isolation Capacitance          | C <sub>IN_OUT</sub> | Unpowered unit measured at 1MHz                                                                 |                    | 380                 |               | pF                    |

| Isolation Resistance           | R <sub>IN_OUT</sub> | Measured at 500V <sub>DC</sub>                                                                  | 10                 |                     |               | ΜΩ                    |

| MTBF                           |                     | MIL-HDBK-217 Plus Parts Count;<br>25°C Ground Benign, Stationary,<br>Indoors / Computer Profile |                    | 9.85                |               | MHrs                  |

|                                |                     | Telcordia Issue 2 - Method I Case III;<br>Ground Benign, Controlled                             |                    | 22.67               |               | MHrs                  |

|                                |                     | cURus, UL 60950-1                                                                               |                    |                     |               |                       |

| Agency Approvals / Standards   |                     | cTÜVus, EN 60950-1                                                                              |                    |                     |               |                       |

| Agency Approvais / Standards   |                     | UKCA, electrical equipment (safety) regu                                                        | lations            |                     |               |                       |

|                                |                     | CE marked for Low Voltage Directive and                                                         | d RoHS Recast Dire | ective, as applicab | е             |                       |

## Using the Control Signals VDR, EN, FLT, TM

#### **VDR: The VTM VDR Supply**

This pin is an input pin which powers the internal bias circuit within the specified voltage range.

Some additional notes on using the VDR pin:

- The VDR voltage must be applied indefinitely allowing for continuous operation for entire input voltage range of VTM.

- The fault response of the VTM module is latching. Recycle of input voltage in presence of VDR is required in order to restart the unit, provided the FLT and EN pins are floating.

#### **FLT: Fault Management**

This pin can be used to accomplish the following functions:

- VTM output disable: FLT pin can be actively pulled down in order to disable the module. The pull down resistance shall be lower than  $25k\Omega$ . The FLT voltage should be lower than the minimum disable threshold as specified in signal characteristics in order to keep the VTM off.

- VTM start up: VTM will start up after FLT signal crosses its maximum undervoltage threshold point. In order to guarantee VTM start up, resistance applied from FLT pin to ground must exceed the minimum external resistance as specified in signal characteristics.

- VTM start up after FLT pulled low: Disabling the VTM by pulling the FLT pin of the VTM low is latching. Recycling the input voltage in presence of VDR is required in order to restart the VTM, provided the EN pin is floating.

- VTMs array fault shut down: In an array, the FLT pin of VTMs should be tied together. In the case of a fault on one of the VTMs, the FLT pin of VTM under fault can pull the common FLT signal low and shut the VTM array off.

- VTMs array start up: In an array, FLT signal can be used as a Power Good/Ready signal to apply the input voltage to the VTM. The FLT signal should be above maximum enable threshold voltage to ensure all VTMs in the array are ready.

#### **TM: Temperature Monitor**

This pin provides a voltage proportional to the absolute temperature of the converter control IC.

It can be used to accomplish the following functions:

- Monitor the control IC temperature: The temperature in Kelvin is equal to the voltage on the TM pin scaled by 100 (i.e., 3.0V = 300K = 27°C). If a heat sink is applied, TM can be used to thermally protect the system.

- Fault detection flag: The TM voltage source is internally turned off as soon as a fault is detected. For system monitoring purposes (microcontroller interface) faults are detected on falling edges of TM signal.

- VTMs array start up: In an array, TM signal can be used as a Power Good/Ready signal to apply the input voltage to the VTM. The TM signal of all VTMs should be high to ensure all VTMs in the array are ready.

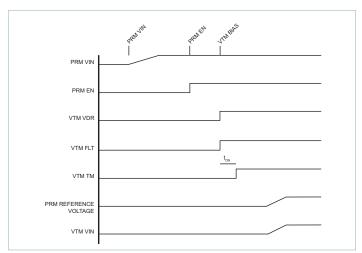

### **VTM Start Up**

The VTM module is designed to operate with an upstream PRM<sup>TM</sup>. Start-up and fault-retry control is primarily managed by the regulator. Soft start is achieved by the PRM output voltage ramp up typically proportional to the internal or external slew rate of the feedback loop reference voltage. (Figure 15)

The VTM input voltage slew rate is the only means to control the inrush current through the VTM into a large VTM output capacitive load.

To start the VTM apply bias voltage to VDR pin. VDR voltage must be applied first to wake up the internal controller. Input voltage, output voltage and overtemperature are all checked prior to powertrain operation. Once faults are checked and only if all faults are cleared the controller initiates the powertrain within a time period specified by  $t_{\text{ON}}$  (see VDR Signal Characteristics).

- A VTM input greater than 1.25V prior to applying a bias voltage is not recommended. Permanent module damage may occur or the module may fail to start.

- A VTM output voltage prior or during a start-up check triggers a reverse inrush protection mode that is cleared a few powertrain cycles after VTM input voltage exceeds the equivalent pre-applied output voltage with respect to the VTM K factor.

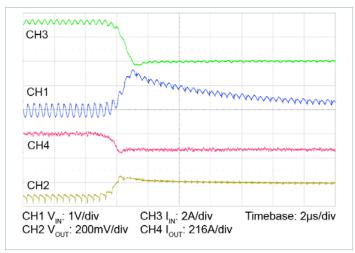

Figure 15 — VTM start up

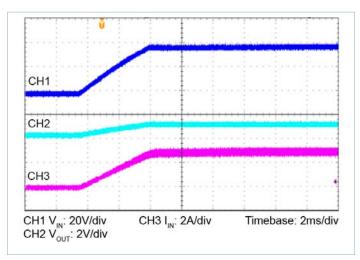

Figure 16 — Typical VTM start up

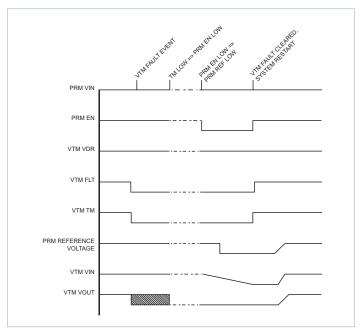

## **VTM Fault Response**

A fault event such as: input or output overvoltage, overtemperature, or FLT pin externally driven low to disable the module triggers a VTM latching shut-down condition. A low VTM  $V_{IN}$  state less than 1.25V or a VDR (5V) recycle is required to clear the fault latch when reapplying VDR. If  $V_{IN}$  is  $\geq 1.25$ V, the module will latch. The powertrain will resume or restart switching only if the fault trigger is not persistent. Typically the TM pin through a 10k $\Omega$  is used to hold the PRM EN low until the VTM faults clear. Once the VTM fault is cleared, the system is allowed to reset by first allowing the PRM EN followed by a reference soft start and VTM  $V_{IN}$  ramp up. It is also possible to connect PRM FLT to VTM FLT to manage interoperability.

Figure 17 — VTM fault response

#### **Protection**

The VTM relies heavily on the upstream PRM and/or system controller for protection from many abnormal events. The designer should insure that the complete system provides the VTM with adequate short circuit and output overcurrent protection. Using a validated reference design is a way to be assured that the VTM is appropriately protected at a system level. For assistance in selecting and implementing a complete reference design, please consult with Vicor Applications Engineering.

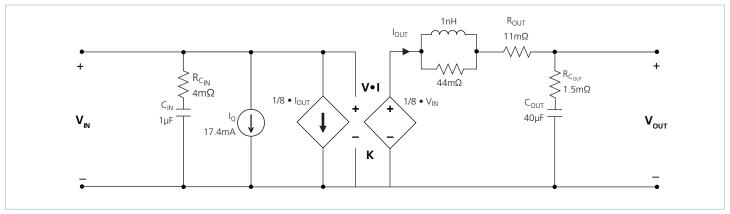

## **Sine Amplitude Converter Point-of-Load Conversion**

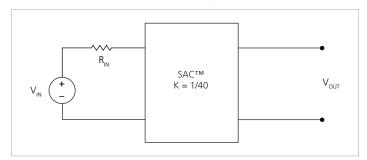

Figure 18 — Sine Amplitude Converter AC model

The Sine Amplitude Converter (SAC<sup>TM</sup>) uses a high frequency resonant tank to move energy from input to output. (The resonant tank is formed by Cr and leakage inductance Lr in the power transformer windings as shown in the VTM Module Block Diagram). The resonant LC tank, operated at high frequency, is amplitude modulated as a function of input voltage and output current. A small amount of capacitance embedded in the input and output stages of the module is sufficient for full functionality and is key to achieving power density.

The SAC can be simplified into the following model:

At no load:

$$V_{OUT} = V_{IN} \bullet K \tag{1}$$

K represents the "turns ratio" of the SAC. Rearranging Equation 1:

$$K = \frac{V_{OUT}}{V_{IN}} \tag{2}$$

In the presence of load,  $V_{\text{OUT}}$  can be approximated as:

$$V_{OUT} = V_{IN} \bullet K - I_{OUT} \bullet R_{OUT}$$

(3)

and I<sub>OUT</sub> can be approximated as:

$$I_{OUT} = \frac{I_{IN} - I_Q}{K} \tag{4}$$

$R_{OUT}$  represents the impedance of the SAC, and is a function of the  $R_{DSON}$  of the input and output MOSFETs and the winding resistance of the power transformer.  $I_Q$  represents the quiescent current of the SAC control and gate drive circuitry.

The use of DC voltage transformation provides additional interesting attributes. Consider an idealized SAC with K = 1/40,  $R_{OUT} = 0\Omega$  and  $I_Q = 0A$ . Equation 3 now becomes Equation 1 and is essentially load independent. In this example, resistor R is now placed in series with  $V_{IN}$  as shown in Figure 19.

Figure 19 — Sine Amplitude Converter with series input resistor

The relationship between V<sub>IN</sub> and V<sub>OUT</sub> becomes:

$$V_{OUT} = (V_{IN} - I_{IN} \bullet R_{IN}) \bullet K \tag{5}$$

Substituting the simplified version of Equation 4 ( $I_0$  is assumed = 0A) into Equation 5 yields:

$$V_{OUT} = V_{IN} \bullet K - I_{OUT} \bullet R_{IN} \bullet K^2 \tag{6}$$

This is similar in form to Equation 3, where  $R_{OUT}$  is used to represent the characteristic impedance of the SAC<sup>TM</sup>. However, in this case a real R on the input side of the SAC is effectively scaled by  $K^2$  with respect to the output.

Assuming that  $R = 1\Omega$ , the effective R as seen from the secondary side is  $0.62m\Omega$ , with K = 1/40 as shown in Figure 19.

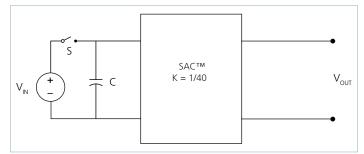

A similar exercise should be performed with the addition of a capacitor or shunt impedance at the input to the SAC. A switch in series with  $V_{\text{IN}}$  is added to the circuit. This is depicted in Figure 20.

Figure 20 — Sine Amplitude Converter with input capacitor

A change in  $V_{\rm IN}$  with the switch closed would result in a change in capacitor current according to the following equation:

$$I_C(t) = C \frac{dV_{IN}}{dt} \tag{7}$$

Assume that with the capacitor charged to  $V_{\text{IN}}$ , the switch is opened and the capacitor is discharged through the idealized SAC. In this case,

$$I_C = I_{OUT} \bullet K \tag{8}$$

Substituting Equation 1 and 8 into Equation 7 reveals:

$$I_{OUT} = \frac{C}{K^2} \bullet \frac{dV_{OUT}}{dt} \tag{9}$$

The equation in terms of the output has yielded a  $K^2$  scaling factor for C, specified in the denominator of the equation.

A K factor less than unity, results in an effectively larger capacitance on the output when expressed in terms of the input. With a K = 1/40 as shown in Figure 23, C =  $1\mu$ F would appear as C =  $1600\mu$ F when viewed from the output.

Low impedance is a key requirement for powering a high-current, low-voltage load efficiently. A switching regulation stage should have minimal impedance while simultaneously providing appropriate filtering for any switched current. The use of a SAC between the regulation stage and the point of load provides a dual benefit of scaling down series impedance leading back to the source and scaling up shunt capacitance or energy storage as a function of its K factor squared. However, the benefits are not useful if the series impedance of the SAC is too high. The impedance of the SAC must be low, i.e., well beyond the crossover frequency of the system.

A solution for keeping the impedance of the SAC low involves switching at a high frequency. This enables small magnetic components because magnetizing currents remain low. Small magnetics mean small path lengths for turns. Use of low-loss core material at high frequencies also reduces core losses.

The two main terms of power loss in the VTM module are:

- No load power dissipation (P<sub>NL</sub>): defined as the power used to power up the module with an enabled powertrain at no load. It includes the components due to input voltage and VDR voltage.

- Resistive loss (R<sub>OUT</sub>): refers to the power loss across the VTM module modeled as pure resistive impedance.

$$P_{DISSIPATED} = P_{NL} + P_{R_{OUT}} \tag{10}$$

Therefore,

$$P_{OUT} = P_{IN} - P_{DISSIPATED} = P_{IN} - P_{NL} - P_{ROUT}$$

$$\tag{11}$$

The above relations can be combined to calculate the overall module efficiency:

$$\eta = \frac{P_{OUT}}{P_{IN}} = \frac{P_{IN} - P_{NL} - P_{ROUT}}{P_{IN}}$$

(12)

$$= \frac{V_{\mathit{IN}} \bullet I_{\mathit{IN}} - P_{\mathit{NL}} - (I_{\mathit{OUT}})^2 \bullet R_{\mathit{OUT}}}{V_{\mathit{IN}} \bullet I_{\mathit{IN}}}$$

$$= 1 - \left(\frac{P_{NL} + (I_{OUT})^2 \cdot R_{OUT}}{V_{IN} \cdot I_{IN}}\right)$$

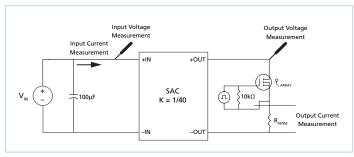

# Open Loop Transient Performance of a Sine Amplitude Converter

The VTM package provides very low parasitic inductance on both the input and output connections. This combined with the use of a high frequency Sine Amplitude Converter topology results in a very low input to output impedance characteristic for the VTM. This low impedance is approximately between 1.2 and 1.5 times  $R_{OUT}$  from DC to approximately 1MHz. This yields significant benefits in transient performance by effectively presenting upstream capacitive energy storage at the output of the VTM will very little intervening impedance. This can be illustrated in the following way. Figure 21 shows a test circuit that applies a 130A load step to a VTM with a K = 1/40. An array of MOSFETs (Q1<sub>ARRAY</sub>) is gated by a function generator to provide a current pulse with a <5 $\mu$ s rise time. The actual output current is measured using  $R_{SFNSF}$ .

Figure 21 — Sine Amplitude Converter with input capacitor

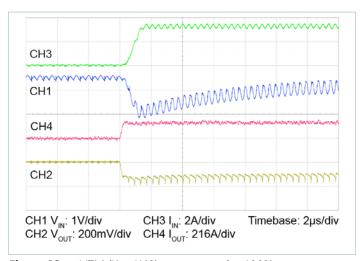

The response of the VTM to a 0-100% load step can be seen in Figure 22 and the VTM response to a 100-0% load step can be seen in Figure 23. There are several important characteristics to note concerning the VTM transient response.

1. The VTM shows a "current multiplier" characteristic where the input and output current are proportional. The input current to the VTM reaches the steady state value within a few switching cycles (~400ns).

**Figure 22** — VTM (K = 1/40) response to 0 − 100% (0 − 130A) load step

**Figure 23** — VTM (K = 1/40) response to a 100 – 0% (130 – 0A) load step

- **2.** The input power supply response is reflected directly to the output of the VTM. The input supply settles within 12µs of the load step and the voltage settling waveform can be clearly seen on the output, scaled by the K factor.

- **3.** The output voltage of the VTM drops in proportion to the output load current. This V<sub>OUT</sub> drop can be expressed as:

$$\Delta V_{out} = \delta \bullet R_{out} \bullet \Delta I_{out}$$

(13)

In this equation  $R_{OUT}$  is the output resistance as specified in the datasheet and  $\delta$  is a scaling factor to compensate for higher order terms in the  $V_{OUT} = V_{IN} \bullet K - I_{OUT} \bullet R_{OUT}$  equation.  $\delta$  is typically between 1.2 and 1.5 and varies based on the model of VTM and the size of the load step.

As a result of these key characteristics in the VTM response, capacitance with ESR >>  $R_{\rm OUT}$  and ESL >>  $L_{\rm OUT\_PAR}$  located at the output of the VTM will not contribute significantly to the transient response of a system. The VTM effectively unburdens the system from needing bypass capacitance for frequency response below 1MHz, leaving only the >1MHz component to require filtering at the point of load.

## **Input and Output Filter Design**

A major advantage of a SACTM system versus a conventional PWM converter is that the former does not require large functional filters. The resonant LC tank, operated at extreme high frequency, is amplitude modulated as a function of input voltage and output current and efficiently transfers charge through the isolation transformer. A small amount of capacitance embedded in the input and output stages of the module is sufficient for full functionality and is key to achieving high power density.

This paradigm shift requires system design to carefully evaluate external filters in order to:

■ Guarantee low source impedance:

To take full advantage of the VTM current multiplier dynamic response, the impedance presented to its input terminals must be low from DC to approximately 5MHz. Input capacitance may be added to improve transient performance or compensate for high source impedance.

■ Further reduce input and/or output voltage ripple without sacrificing dynamic response:

Given the wide bandwidth of the VTM module, the source response is generally the limiting factor in the overall system response. Anomalies in the response of the source will appear at the output of the VTM module multiplied by its K factor.

Protect the module from overvoltage transients imposed by the system that would exceed maximum ratings and cause failures:

The module input/output voltage ranges shall not be exceeded. An internal overvoltage lockout function prevents operation outside of the normal operating input range. Even when disabled, the powertrain is exposed to the applied voltage and power MOSFETs must withstand it.

Common mode sensitive applications may require an external bypass capacitor from –IN to –OUT. The common mode voltage can be approximated to be  $V_{IN} \bullet K \bullet (2)^{-1/2}$ . Generally a series stacked ceramic capacitor with a typical value of 5400pF is found to effectively reduce this noise.

# Capacitive Filtering Considerations for a Sine Amplitude Converter

It is important to consider the impact of adding input and output capacitance to a Sine Amplitude Converter on the system as a whole. Both the capacitance value and the effective impedance of the capacitor must be considered.

A Sine Amplitude Converter has a DC  $R_{OUT}$  value which has already been discussed. The AC  $R_{OUT}$  of the SAC contains several terms:

- Resonant tank impedance

- Input lead inductance and internal capacitance

- Output lead inductance and internal capacitance

The values of these terms are shown in the behavioral mode. It is important to note on which side of the transformer these impedances appear and how they reflect across the transformer given the K factor.

The overall AC impedance varies from model to model. For most models it is dominated by DC  $R_{OUT}$  value from DC to beyond 500kHz. The behavioral model should be used to approximate the AC impedance of the specific model.

Any capacitors placed at the output of the VTM reflect back to the input of the VTM module by the square of the K factor (Equation 9) with the impedance of the VTM module appearing in series. It is very important to keep this in mind when using a PRM<sup>TM</sup> regulator to power the VTM module. Most PRM modules have a limit on the maximum amount of capacitance that can be applied to the output. This capacitance includes both the PRM output capacitance and the VTM module output capacitance reflected back to the input. In PRM remote sense applications, it is important to consider the reflected value of VTM module output capacitance when designing and compensating the PRM control loop.

Capacitance placed at the input of the VTM module appear to the load reflected by the K factor with the impedance of the VTM module in series. In step-down ratios, the effective capacitance is increased by the K factor. The effective ESR of the capacitor is decreased by the square of the K factor, but the impedance of the module appears in series. Still, in most step-down VTM modules an electrolytic capacitor placed at the input of the module will have a lower effective impedance compared to an electrolytic capacitor placed at the output. This is important to consider when placing capacitors at the output of the module. Even though the capacitor may be placed at the output, the majority of the AC current will be sourced from the lower impedance, which in most cases will be the module. This should be studied carefully in any system design using a module. In most cases, it should be clear that electrolytic output capacitors are not necessary to design a stable, well-bypassed system.

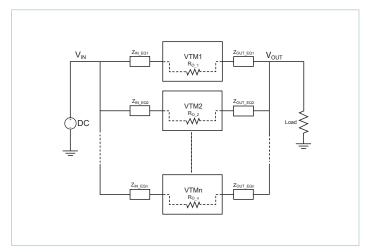

#### **Current Sharing**

The SAC<sup>TM</sup> topology bases its performance on efficient transfer of energy through a transformer without the need of closed loop control. For this reason, the transfer characteristic can be approximated by an ideal current multiplier with some resistive drop and positive temperature coefficient.

This type of characteristic is close to the impedance characteristic of a DC power distribution system, both in behavior (AC dynamic) and absolute value (DC dynamic).

When connected in an array with the same K factor, the VTM module will inherently share the load current (typically 5%) with parallel units according to the equivalent impedance divider that the system implements from the power source to the point of load.

Some general recommendations to achieve matched array impedances:

- Dedicate common copper planes within the PCB to deliver and return the current to the modules.

- Provide the PCB layout as symmetric as possible.

- Apply same input / output filters (if present) to each unit.

For further details see:

AN:016 Using BCM<sup>®</sup> Bus Converters in High Power Arrays.

Figure 24 — VTM current multiplier array

#### **Fuse Selection**

The VTM is not internally fused, see safety approvals for required fusing.

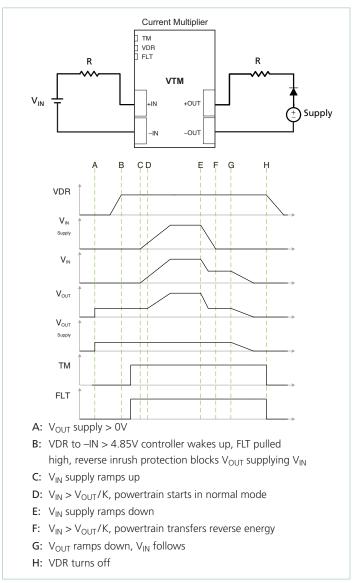

#### **Reverse Inrush Current Protection**

The VTM provides reverse inrush protection which prevents reverse current flow until the input voltage is high enough to first establish current flow in the forward direction. In the event that there is a DC voltage present on the output before the VTM module is powered up, this feature protects sensitive loads from excessive dV/dt during power up as shown in Figure 25.

If a voltage is present at the output of the VTM module which satisfies the condition  $V_{OUT} > V_{IN} \bullet K$  after a successful power up the energy will be transferred from secondary to primary. The input to output ratio of the VTM module will be maintained. The VTM module will continue to operate in reverse as long as the input and output voltages are within the specified range. The VTM has not been qualified for continuous reverse operation.

Figure 25 — Reverse inrush protection

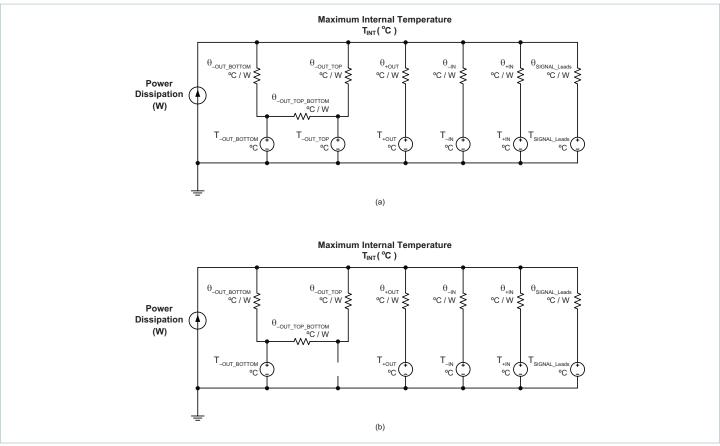

## **Thermal Design**

Figure 26 shows a thermal impedance model that can estimate the maximum temperature of the highest temperature component for a given operating condition ( $T_{INT}$ ).  $T_{INT}$  must be within the specified operating temperature grade of the product. Use of

non-conductive TIM (Thermal Interface Material) is required to prevent shorting conductive surfaces on case. Thermal model (a) and (b) below represent similar cooling conditions shown in Figure 1.

Figure 26 — Thermal circuit model

#### Where the symbol in Figure 27 is defined as the following:

| $\theta_{\text{-OUT\_BOTTOM}}$     | is defined as the thermal resistance from the maximum internal temperature to the –OUT thermal pads and –OUT pads shown on the recommended land pattern. |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\theta_{\text{-OUT\_TOP}}$        | is defined as the thermal resistance from the maximum internal temperature to the –OUT copper on top of the VTM.                                         |

| $\theta_{	ext{-OUT\_TOP\_BOTTOM}}$ | is defined as the thermal resistance from the -OUT_TOP to the -OUT_BOTTOM.                                                                               |

| $\theta_{+OUT}$                    | is defined as the thermal resistance from the maximum internal temperature to the +OUT pads shown on the recommended land pattern.                       |

| $\theta_{-IN}$                     | is defined as the thermal resistance from the maximum internal temperature to the –IN pads shown on the recommended land pattern.                        |

| $\theta_{+\text{IN}}$              | is defined as the thermal resistance from the maximum internal temperature to the +IN pads shown on the recommended land pattern.                        |

| $\theta_{SIGNAL\_Leads}$           | is defined as the thermal resistance from the maximum internal temperature to the SIGNAL_Leads pads shown on the recommended land pattern.               |

|                                                       | Thermal Impedance |    |    |    |    |     |  |  |  |  |  |

|-------------------------------------------------------|-------------------|----|----|----|----|-----|--|--|--|--|--|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |                   |    |    |    |    |     |  |  |  |  |  |

| 4.2                                                   | 5.2               | 23 | 11 | 68 | 58 | n/a |  |  |  |  |  |

**Table 1** — Thermal impedance

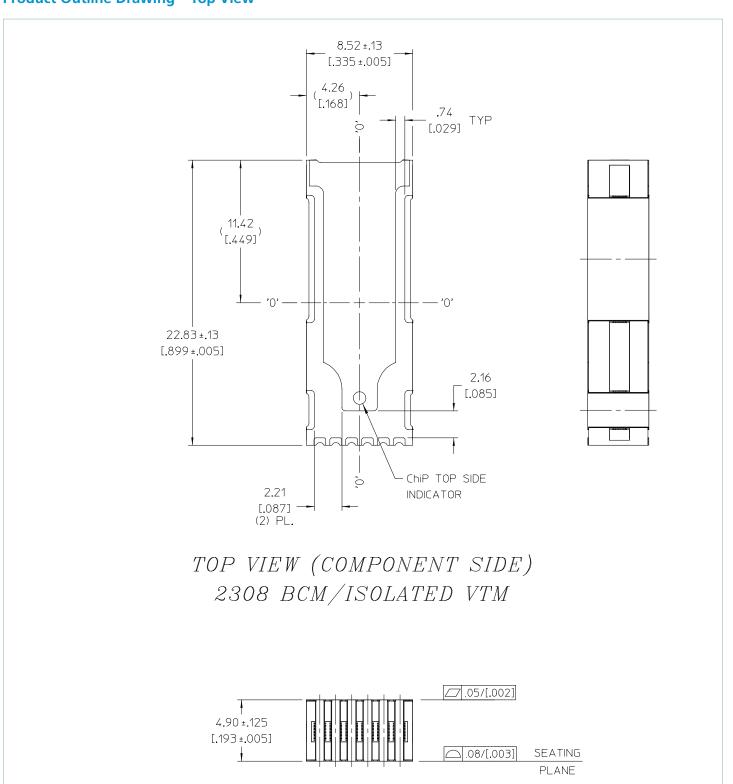

# **Product Outline Drawing – Top View**

UNLESS OTHERWISE SPECIFIED DIMENSIONS ARE MM [INCH]

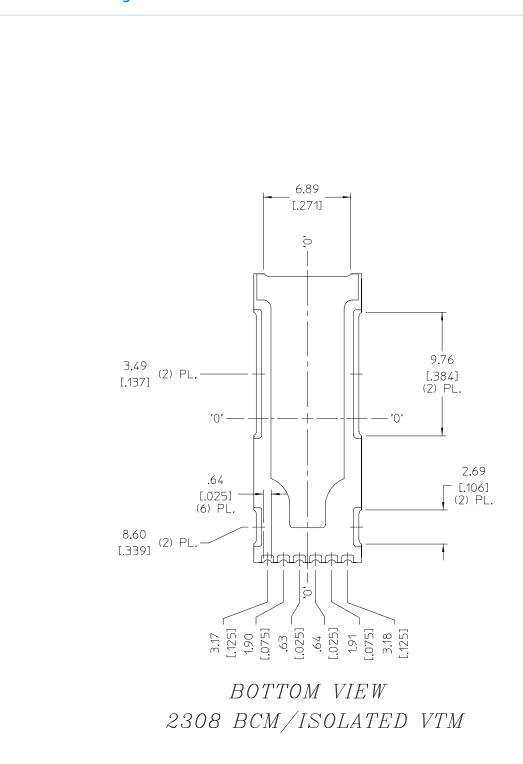

# **Product Outline Drawing – Bottom View**

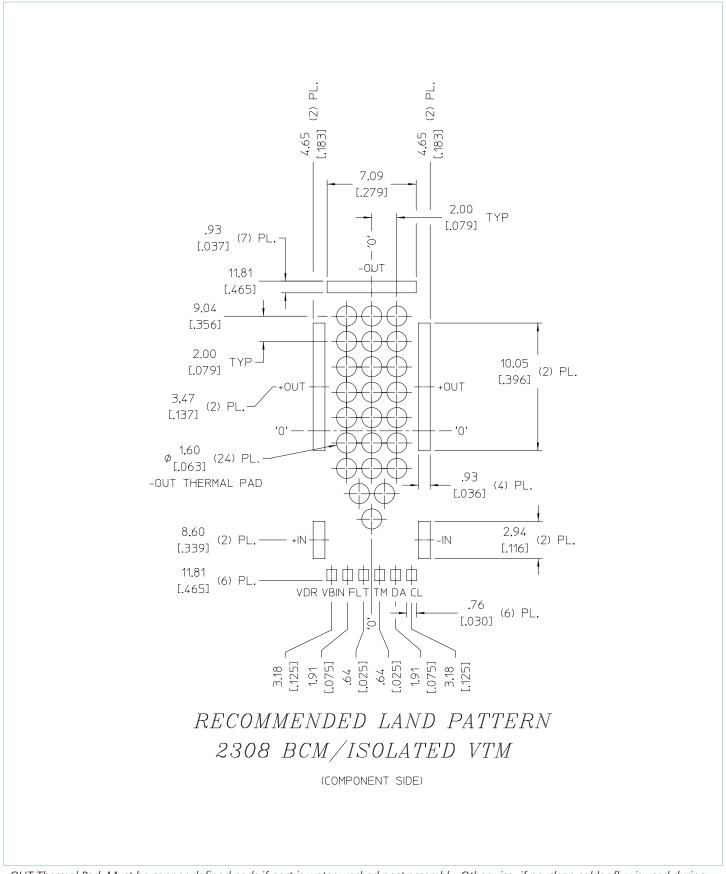

## **Recommended Land Pattern**

-OUT Thermal Pad: Must be copper-defined pads if part is water washed post assembly. Otherwise, if no-clean solder flux is used during assembly, thermal pads may be solder-mask-defined openings.

# **Revision History**

| Revision | Date     | Description                                                              | Page Number(s) |

|----------|----------|--------------------------------------------------------------------------|----------------|

| 1.0      | 02/27/19 | Initial release                                                          | n/a            |

| 1.1      | 05/03/19 | Updated absolute max rating (+OUT to –OUT)                               | 4              |

| 1.2      | 02/05/20 | Updated isolation resistance specification                               | 11             |

| 1.3      | 06/15/20 | Internal bias function removed; VBIN pin is made a "No Connect" pin      | 2, 3, 4, 7, 11 |

| 1.4      | 02/07/22 | Revised agency approvals                                                 | 1, 10          |

| 1.5      | 12/01/22 | Clarified overtemperature fault                                          | 5              |

| 1.6      | 10/13/23 | Revised overcurrent trip typical and max<br>Revised VDR current draw max | 5<br>7         |

Note: page removed in Rev 1.3

# Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication. Vicor reserves the right to make changes to any products, specifications, and product descriptions at any time without notice. Information published by Vicor has been checked and is believed to be accurate at the time it was printed; however, Vicor assumes no responsibility for inaccuracies. Testing and other quality controls are used to the extent Vicor deems necessary to support Vicor's product warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

Specifications are subject to change without notice.

Visit <a href="https://www.vicorpower.com/dc-dc-converters-board-mount/vtm">https://www.vicorpower.com/dc-dc-converters-board-mount/vtm</a> for the latest product information.

#### **Vicor's Standard Terms and Conditions and Product Warranty**

All sales are subject to Vicor's Standard Terms and Conditions of Sale, and Product Warranty which are available on Vicor's webpage (https://www.vicorpower.com/termsconditionswarranty) or upon request.

## **Life Support Policy**

VICOR'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF VICOR CORPORATION. As used herein, life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness. Per Vicor Terms and Conditions of Sale, the user of Vicor products and components in life support applications assumes all risks of such use and indemnifies Vicor against all liability and damages.

#### **Intellectual Property Notice**

Vicor and its subsidiaries own Intellectual Property (including issued U.S. and Foreign Patents and pending patent applications) relating to the products described in this data sheet. No license, whether express, implied, or arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Interested parties should contact Vicor's Intellectual Property Department.

The products described on this data sheet are protected by the following U.S. Patents Numbers:

5,945,130; 6,403,009; 6,710,257; 6,911,848; 6,930,893; 6,934,166; 6,940,013; 6,969,909; 7,038,917; 7,145,186; 7,166,898; 7,187,263; 7,202,646; 7,361,844; 9,166,481; 9,516,761; D496,906; D505,114; D506,438; D509,472; and for use under 6,975,098 and 6,984,965.

Contact Us: https://www.vicorpower.com/contact-us

#### **Vicor Corporation**

25 Frontage Road Andover, MA, USA 01810 Tel: 800-735-6200 Fax: 978-475-6715 www.vicorpower.com

#### email

Customer Service: <u>custserv@vicorpower.com</u> Technical Support: <u>apps@vicorpower.com</u>

©2019 – 2023 Vicor Corporation. All rights reserved. The Vicor name is a registered trademark of Vicor Corporation.

All other trademarks, product names, logos and brands are property of their respective owners.